## Is Now Part of

# ON Semiconductor®

To learn more about ON Semiconductor, please visit our website at <a href="https://www.onsemi.com">www.onsemi.com</a>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, emplo

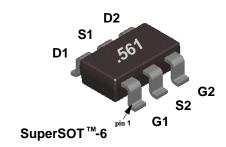

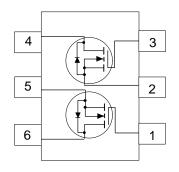

## FDC6561AN

## **Dual N-Channel Logic Level PowerTrench™ MOSFET**

## **General Description**

These N-Channel Logic Level MOSFETs are produced using Fairchild Semiconductor's advanced PowerTrench process that has been especially tailored to minimize the on-state resistance and yet maintain low gate charge for superior switching performance.

These devices are well suited for all applications where small size is desireable but especially low cost DC/DC conversion in battery powered systems.

#### **Features**

- 2.5 A, 30 V.  $R_{DS(ON)} = 0.095 \Omega$  @  $V_{GS} = 10 V$  $R_{DS(ON)} = 0.145 \Omega$  @  $V_{GS} = 4.5 V$

- Very fast switching.

- Low gate charge (2.1nC typical).

- SuperSOT<sup>™</sup>-6 package: small footprint (72% smaller than standard SO-8); low profile (1mm thick).

## Absolute Maximum Ratings

$T_A = 25$ °C unless otherwise note

| Symbol                           | Parameter                               |                  | Ratings    | Units |

|----------------------------------|-----------------------------------------|------------------|------------|-------|

| V <sub>DSS</sub>                 | Drain-Source Voltage                    |                  | 30         | V     |

| $V_{GSS}$                        | Gate-Source Voltage - Continuous        |                  | ±20        | V     |

| I <sub>D</sub>                   | Drain Current - Continuous              |                  | 2.5        | А     |

|                                  | - Pulsed                                |                  | 10         |       |

| P <sub>D</sub>                   | Maximum Power Dissipation               | (Note 1a)        | 0.96       | W     |

|                                  |                                         | (Note 1b)        | 0.9        |       |

|                                  |                                         | (Note 1c)        | 0.7        |       |

| T <sub>J</sub> ,T <sub>STG</sub> | Operating and Storage Temperature Range |                  | -55 to 150 | ℃     |

| THERMA                           | AL CHARACTERISTICS                      |                  |            |       |

| $R_{\theta JA}$                  | Thermal Resistance, Junction-to-An      | nbient (Note 1a) | 130        | °C/W  |

| $R_{\theta JC}$                  | Thermal Resistance, Junction-to-Ca      | ISE (Note 1)     | 60         | °C/W  |

| Symbol                           | Parameter                              | Conditions                                              | Min | Тур   | Max   | Units |

|----------------------------------|----------------------------------------|---------------------------------------------------------|-----|-------|-------|-------|

| OFF CHAR                         | ACTERISTICS                            | •                                                       | •   | •     | •     | •     |

| BV <sub>DSS</sub>                | Drain-Source Breakdown Voltage         | $V_{GS} = 0 \text{ V}, I_D = 250 \mu\text{A}$           | 30  |       |       | V     |

| $\Delta BV_{DSS}/\Delta T_{J}$   | Breakdown Voltage Temp. Coefficient    | I <sub>D</sub> = 250 μA, Referenced to 25 °C            |     | 23.6  |       | mV/°C |

| I <sub>DSS</sub>                 | Zero Gate Voltage Drain Current        | $V_{DS} = 24 \text{ V}, \ V_{GS} = 0 \text{ V}$         |     |       | 1     | μΑ    |

|                                  |                                        | T <sub>J</sub> = 55 °C                                  |     |       | 10    | μΑ    |

| I <sub>GSSF</sub>                | Gate - Body Leakage, Forward           | $V_{GS} = 20 \text{ V}, V_{DS} = 0 \text{ V}$           |     |       | 100   | nA    |

| I <sub>GSSR</sub>                | Gate - Body Leakage, Reverse           | $V_{GS} = -20 \text{ V}, V_{DS} = 0 \text{ V}$          |     |       | -100  | nA    |

| ON CHARA                         | CTERISTICS (Note 2)                    |                                                         | •   | •     |       | •     |

| V <sub>GS(th)</sub>              | Gate Threshold Voltage                 | $V_{DS} = V_{GS}, I_{D} = 250 \mu\text{A}$              | 1   | 1.8   | 3     | V     |

| $\Delta V_{GS(th)}/\Delta T_{J}$ | Gate Threshold VoltageTemp.Coefficient | I <sub>D</sub> = 250 μA, Referenced to 25 °C            |     | -4    |       | mV/°C |

| R <sub>DS(ON)</sub>              | Static Drain-Source On-Resistance      | $V_{GS} = 10 \text{ V}, I_{D} = 2.5 \text{ A}$          |     | 0.082 | 0.095 | Ω     |

| ()                               |                                        | T <sub>J</sub> = 125 °C                                 |     | 0.122 | 0.152 |       |

|                                  |                                        | $V_{GS} = 4.5 \text{ V}, I_{D} = 2.0 \text{ A}$         |     | 0.113 | 0.145 |       |

| I <sub>D(on)</sub>               | On-State Drain Current                 | $V_{GS} = 10 \text{ V}, V_{DS} = 5 \text{ V}$           | 10  |       |       | Α     |

| g <sub>FS</sub>                  | Forward Transconductance               | $V_{DS} = 5 \text{ V}, I_{D} = 2.5 \text{ A}$           |     | 5     |       | S     |

| DYNAMIC C                        | HARACTERISTICS                         | •                                                       | •   |       | •     |       |

| C <sub>iss</sub>                 | Input Capacitance                      | $V_{DS} = 15 \text{ V}, \ V_{GS} = 0 \text{ V},$        |     | 220   |       | pF    |

| C <sub>oss</sub>                 | Output Capacitance                     | f = 1.0 MHz                                             |     | 50    |       | pF    |

| C <sub>rss</sub>                 | Reverse Transfer Capacitance           |                                                         |     | 25    |       | pF    |

| SWITCHING                        | CHARACTERISTICS (Note 2)               |                                                         |     |       |       |       |

| t <sub>D(on)</sub>               | Turn - On Delay Time                   | $V_{DD} = 5 \text{ V}, \ I_{D} = 1 \text{ A},$          |     | 6     | 12    | ns    |

| t,                               | Turn - On Rise Time                    | $V_{GS} = 10 \text{ V}, R_{GEN} = 6 \Omega$             |     | 10    | 18    | ns    |

| t <sub>D(off)</sub>              | Turn - Off Delay Time                  |                                                         |     | 12    | 22    | ns    |

| t,                               | Turn - Off Fall Time                   |                                                         |     | 2     | 6     | ns    |

| $Q_g$                            | Total Gate Charge                      | $V_{DS} = 15 \text{ V}, I_{D} = 2.5 \text{ A}$          |     | 2.3   | 3.2   | nC    |

| $Q_{gs}$                         | Gate-Source Charge                     | V <sub>GS</sub> = 5 V                                   |     | 0.7   | 1     | nC    |

| $Q_{gd}$                         | Gate-Drain Charge                      |                                                         |     | 0.9   | 1.3   | nC    |

| DRAIN-SOU                        | RCE DIODE CHARACTERISTICS              |                                                         |     |       |       |       |

| l <sub>s</sub>                   | Continuous Source Diode Current        |                                                         |     |       | 0.75  | Α     |

| V <sub>SD</sub>                  | Drain-Source Diode Forward Voltage     | V <sub>GS</sub> = 0 V, I <sub>S</sub> = 0.75 A (Note 2) |     | 0.78  | 1.2   | V     |

#### Notes

- 1.  $R_{\mu i \lambda}$  is the sum of the junction-to-case and case-to-ambient thermal resistance where the case thermal reference is defined as the solder mounting surface of the drain pins.  $R_{\mu i C}$  is guaranteed by design while  $R_{\mu C L}$  is determined by the user's board design.

- 2. Pulse Test: Pulse Width  $\leq$  300 $\mu$ s, Duty Cycle  $\leq$  2.0%.

a. 130°C/W on a 0.125 in² pad of 2oz copper.

b. 140°C/W on a 0.005 in² pad of 2oz copper.

. 180°C/W on a minimum pad.

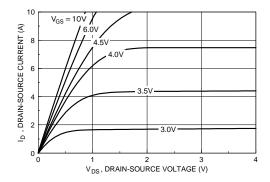

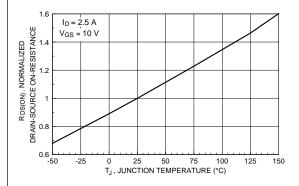

## **Typical Electrical Characteristics**

Figure 1. On-Region Characteristics.

Figure 3. On-Resistance Variation with Temperature.

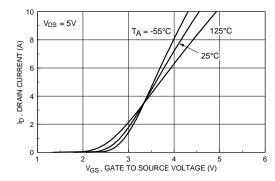

Figure 5.Transfer Characteristics.

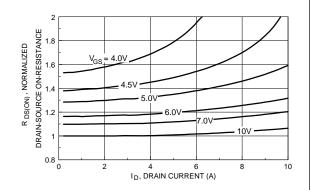

Figure 2. On-Resistance Variation with Drain Current and Gate Voltage.

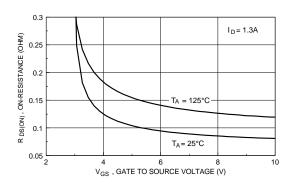

Figure 4. On-Resistance Variation with Gate-to-Source Voltage.

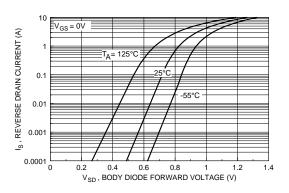

Figure 6. Body Diode Forward Voltage

Variation with Source Current

and Temperature.

## **Typical Electrical Characteristics** (continued)

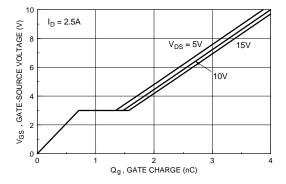

Figure 7. Gate Charge Characteristics.

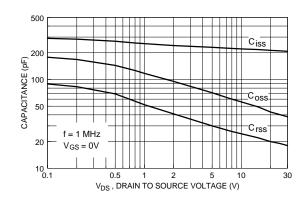

Figure 8. Capacitance Characteristics.

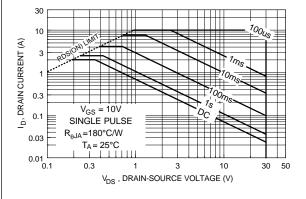

SINGLE PULSE — R<sub>θJA</sub>=180°C/W — T<sub>A</sub>= 25°C — R<sub>θJA</sub>=180°C/W — R<sub>θJA</sub>=180°C

Figure 9. Maximum Safe Operating Area.

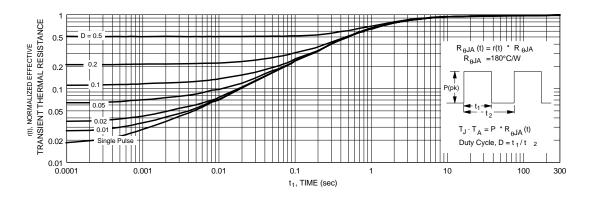

Figure 10. Single Pulse Maximum Power Dissipation.

Figure 11. Transient Thermal Response Curve.

Thermal characterization performed using the conditions described in Note 1c.

Transient thermal response will change depending on the circuit board design.

## **TRADEMARKS**

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

CROSSVOLT<sup>TM</sup> POP<sup>TM</sup>

E<sup>2</sup>CMOS<sup>™</sup> PowerTrench<sup>™</sup>

FACT<sup>TM</sup> QS<sup>TM</sup>

$\begin{array}{lll} \mathsf{FACT} \ \mathsf{Quiet} \ \mathsf{Series^{\mathsf{TM}}} & \mathsf{Quiet} \ \mathsf{Series^{\mathsf{TM}}} \\ \mathsf{FAST}^{\otimes} & \mathsf{SuperSOT^{\mathsf{TM}}}\text{-}3 \\ \mathsf{FASTr^{\mathsf{TM}}} & \mathsf{SuperSOT^{\mathsf{TM}}}\text{-}6 \\ \mathsf{GTO^{\mathsf{TM}}} & \mathsf{SuperSOT^{\mathsf{TM}}}\text{-}8 \\ \mathsf{HiSeC^{\mathsf{TM}}} & \mathsf{TinyLogic^{\mathsf{TM}}} \\ \end{array}$

#### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Datasheet Identification | Product Status            | Definition                                                                                                                                                                                                            |

|--------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or<br>In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                    |

| Preliminary              | First Production          | This datasheet contains preliminary data, and supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design. |

| No Identification Needed | Full Production           | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.                                                       |

| Obsolete                 | Not In Production         | This datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor. The datasheet is printed for reference information only.                                                   |

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

## **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81–3–5817–1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative