## Synchronous Four Switch Buck-Boost Analog Front End

### Features

- AEC-Q100 Automotive Qualified, See Product Identification System

- 100W USB-PD/180W EPR with PPS Support

- 12-Bit Resolution for Voltage and Current Settings and Measurements Exceeding USB-PD PPS Requirements

- Accuracy of the Output Voltage Setting of 2% (Closed Loop) from Device to Device Over Output Voltage Range and Temperature

- Accuracy of the Output Current Setting of 3% (Closed Loop) from Device to Device Over Output Voltage Range and Temperature

- Input Voltage: +4.5V to +42V

- Fully Configurable:

- Configurable protections: input and output over current, input over/under voltage, output over/under voltage, load dump, overtemperature, internal regulator fault

- Configurable output: constant current operation, constant voltage operation

- Adjustable frequency

- Dynamically configurable by I<sup>2</sup>C

- · Synchronous 4-Switch Buck/Boost Architecture

- Buck mode operation when  $V_{OUT} < V_{IN}$

- Boost mode operation when V<sub>OUT</sub> > V<sub>IN</sub>

- Buck/Boost operation when V<sub>OUT</sub> ≈ V<sub>IN</sub>

- Adjustable Output Range, 3V to 36V

- Internal LDOs and MOSFET Drivers

- High Accuracy Internal Divider to Set Full Range Output Voltage Without External Resistors

- Accuracy of Input and Output Voltage Measurement of 2% from Device to Device Over Output Voltage Range and Temperature

- Accuracy of the Output Current Measurement of 3% from Device to Device Over Output Voltage Range and Temperature

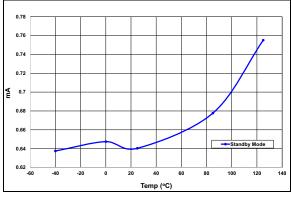

- · Low Quiescent Current in Shutdown Mode

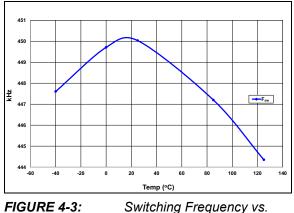

- Switching Frequency Range of 300 kHz to 500 kHz

- Tolerant in Nonoperating 42V Automotive Load Dump Condition

- USB Power Delivery Support:

- High output impedance when stopped

- Output discharge function

- Output overcurrent, overload and short-circuit in accordance with USB power delivery

- Regulation mode (voltage/current) detection

#### **Device Overview**

The MCP19061 is a highly integrated, mixed-signal four switch buck-boost controller that operates from +4.5V to +36V and can withstand up to +42V non-operating.

The MCP19061 features a digital PWM controller with a serial communication bus for external programmability and reporting.

Various enhancements were added to the MCP19061 to provide USB-PD compatibility with minimum external components along with improving calibration, increasing accuracy and providing greater flexibility.

Complete customization of device operating parameters, start-up or shutdown profiles, protection levels and fault handling procedures are accomplished by internal digital registers.

An integrated high accuracy reference voltage is used for setting output current or voltage. Internal input and output dividers facilitate the design while maintaining high accuracy. High accuracy CSA allows precision current regulation and measurement.

The MCP19061 device contains 3 internal LDOs. A 5V LDO (VDD) is used to power internal analog and gate driver circuits and provide 5V externally. A 4V LDO (AVDD) is used to power the internal analog circuitry. A 1.8V LDO is used to supply the internal logic circuitry.

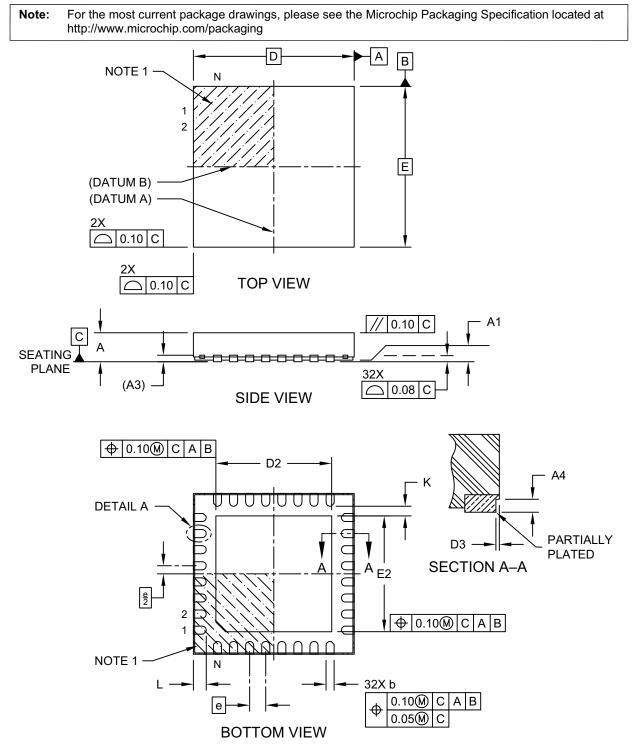

The MCP19061 is packaged in a 32-lead 5 mm x 5 mm VQFN.

System designers have the ability to configure application-specific features allowing users of the MCP19061 device to save on costly board real estate and additional component costs.

A high speed (1 MHz) I<sup>2</sup>C serial bus is used for device communications from the MCP19061 to the system controller.

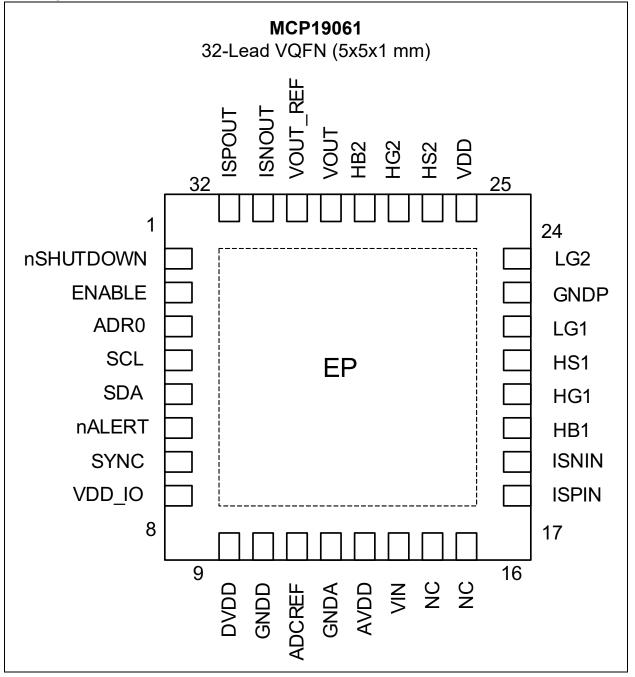

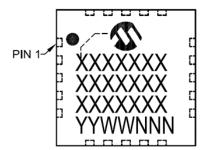

### **Pin Diagram**

| input and shall be grounded)8VDD_IODigital interface supply pin9DVDDOutput of the digital voltage regulator. Connect a capacitor to GNDD10GNDDDigital ground11ADCREFAnalog to digital converters reference12GNDAAnalog ground13AVDDOutput of the analog voltage regulator. Connect a capacitor to GNDA14VINChip supply input. Connect a capacitor to GNDA15NCNot connected16NCNot connected17ISPINPositive connection of the input current sense amplifier18ISNINNegative connection of the input current sense amplifier19HB1Bootstrap supply 1. Connect a capacitor between this pin and HS120HG1Output of the high side driver 121HS1Connect to the source of the high side 1 MOS22LG1Output of the low side driver 123GNDPPower ground24LG2Output of the low side driver 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IABLE 1:         MCP19061 PINOUT DESCRIPTION (SUMMARY) |           |                                                                                                                   |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 2       ENABLE       Enable pin. Starts the power train         3       ADR0       I <sup>2</sup> C address setting pin. Connect a resistor to GNDA         4       SCL       I <sup>2</sup> C clock         5       SDA       I <sup>2</sup> C data         6       nALERT       Internal events detect pin         7       SYNC       Configurable input or output synchronization pin (if not used shall be configure input and shall be grounded)         8       VDD_IO       Digital interface supply pin         9       DVDD       Output of the digital voltage regulator. Connect a capacitor to GNDD         10       GNDD       Digital ground         11       ADCREF       Analog to digital converters reference         12       GNDA       Analog to digital converters reference         13       AVDD       Output of the analog voltage regulator. Connect a capacitor to GNDA         14       VIN       Chip supply input. Connect a capacitor to GNDP         15       NC       Not connected         16       NC       Not connected         17       ISPIN       Positive connection of the input current sense amplifier         19       HB1       Bootstrap supply 1. Connect a capacitor between this pin and HS1         20       HG1       Output of the high side driver 1          | Pin Number                                             | Pin Name  | Description                                                                                                       |  |  |  |  |  |

| 3       ADR0       I <sup>2</sup> C address setting pin. Connect a resistor to GNDA         4       SCL       I <sup>2</sup> C clock         5       SDA       I <sup>2</sup> C data         6       nALERT       Internal events detect pin         7       SYNC       Configurable input or output synchronization pin (if not used shall be configure input and shall be grounded)         8       VDD_IO       Digital interface supply pin         9       DVDD       Output of the digital voltage regulator. Connect a capacitor to GNDD         10       GNDD       Digital ground         11       ADCREF       Analog to digital converters reference         12       GNDA       Analog ground         13       AVDD       Output of the analog voltage regulator. Connect a capacitor to GNDA         14       VIN       Chip supply input. Connect a capacitor to GNDA         14       VIN       Chip supply input. Connect a capacitor to GNDP         15       NC       Not connected         16       NC       Not connection of the input current sense amplifier         19       HB1       Bootstrap supply 1. Connect a capacitor between this pin and HS1         20       HG1       Output of the high side driver 1         21       HS1       Connect to the source of the high side 1 MOS | 1                                                      | nSHUTDOWN | Shutdown pin. Pull low to put the device in low power mode                                                        |  |  |  |  |  |

| 4       SCL       i <sup>2</sup> C clock         5       SDA       i <sup>2</sup> C data         6       nALERT       Internal events detect pin         7       SYNC       Configurable input or output synchronization pin (if not used shall be configure input and shall be grounded)         8       VDD_IO       Digital interface supply pin         9       DVDD       Output of the digital voltage regulator. Connect a capacitor to GNDD         10       GNDD       Digital ground         11       ADCREF       Analog to digital converters reference         12       GNDA       Analog ground         13       AVDD       Output of the analog voltage regulator. Connect a capacitor to GNDA         14       VIN       Chip supply input. Connect a capacitor to GNDA         14       VIN       Chip supply input. Connect a capacitor to GNDP         15       NC       Not connected         16       NC       Not connection of the input current sense amplifier         19       HB1       Bootstrap supply 1. Connect a capacitor between this pin and HS1         20       HG1       Output of the high side driver 1         21       HS1       Connect to the source of the high side 1 MOS         22       LG1       Output of the low side driver 1         23                       | 2                                                      | ENABLE    | Enable pin. Starts the power train                                                                                |  |  |  |  |  |

| 5SDAI²C data6nALERTInternal events detect pin7SYNCConfigurable input or output synchronization pin (if not used shall be configure<br>input and shall be grounded)8VDD_IODigital interface supply pin9DVDDOutput of the digital voltage regulator. Connect a capacitor to GNDD10GNDDDigital ground11ADCREFAnalog to digital converters reference12GNDAAnalog ground13AVDDOutput of the analog voltage regulator. Connect a capacitor to GNDA14VINChip supply input. Connect a capacitor to GNDP15NCNot connected16NCNot connection of the input current sense amplifier18ISNINNegative connection of the input current sense amplifier19HB1Bootstrap supply 1. Connect a capacitor between this pin and HS120HG1Output of the source of the high side 1 MOS22LG1Output of the low side driver 123GNDPPower ground24LG2Output of the low side driver 2                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3                                                      | ADR0      | I <sup>2</sup> C address setting pin. Connect a resistor to GNDA                                                  |  |  |  |  |  |

| 6       nALERT       Internal events detect pin         7       SYNC       Configurable input or output synchronization pin (if not used shall be configure input and shall be grounded)         8       VDD_IO       Digital interface supply pin         9       DVDD       Output of the digital voltage regulator. Connect a capacitor to GNDD         10       GNDD       Digital ground         11       ADCREF       Analog to digital converters reference         12       GNDA       Analog ground         13       AVDD       Output of the analog voltage regulator. Connect a capacitor to GNDA         14       VIN       Chip supply input. Connect a capacitor to GNDA         15       NC       Not connected         16       NC       Not connected         17       ISPIN       Positive connection of the input current sense amplifier         18       ISNIN       Negative connection of the input current sense amplifier         19       HB1       Bootstrap supply 1. Connect a capacitor between this pin and HS1         20       HG1       Output of the high side driver 1         21       HS1       Connect to the source of the high side 1 MOS         22       LG1       Output of the low side driver 1         23       GNDP       Power ground                              | 4                                                      | SCL       | I <sup>2</sup> C clock                                                                                            |  |  |  |  |  |

| 7       SYNC       Configurable input or output synchronization pin (if not used shall be configure input and shall be grounded)         8       VDD_IO       Digital interface supply pin         9       DVDD       Output of the digital voltage regulator. Connect a capacitor to GNDD         10       GNDD       Digital ground         11       ADCREF       Analog to digital converters reference         12       GNDA       Analog ground         13       AVDD       Output of the analog voltage regulator. Connect a capacitor to GNDA         14       VIN       Chip supply input. Connect a capacitor to GNDA         15       NC       Not connected         16       NC       Not connected         17       ISPIN       Positive connection of the input current sense amplifier         18       ISNIN       Negative connection of the input current sense amplifier         19       HB1       Bootstrap supply 1. Connect a capacitor between this pin and HS1         20       HG1       Output of the high side driver 1         21       HS1       Connect to the source of the high side 1 MOS         22       LG1       Output of the low side driver 1         23       GNDP       Power ground         24       LG2       Output of the low side driver 2                           | 5                                                      | SDA       | l <sup>2</sup> C data                                                                                             |  |  |  |  |  |

| input and shall be grounded)8VDD_IODigital interface supply pin9DVDDOutput of the digital voltage regulator. Connect a capacitor to GNDD10GNDDDigital ground11ADCREFAnalog to digital converters reference12GNDAAnalog ground13AVDDOutput of the analog voltage regulator. Connect a capacitor to GNDA14VINChip supply input. Connect a capacitor to GNDA15NCNot connected16NCNot connected17ISPINPositive connection of the input current sense amplifier18ISNINNegative connection of the input current sense amplifier19HB1Bootstrap supply 1. Connect a capacitor between this pin and HS120HG1Output of the high side driver 121HS1Connect to the source of the high side 1 MOS22LG1Output of the low side driver 123GNDPPower ground24LG2Output of the low side driver 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6                                                      | nALERT    | Internal events detect pin                                                                                        |  |  |  |  |  |

| 9DVDDOutput of the digital voltage regulator. Connect a capacitor to GNDD10GNDDDigital ground11ADCREFAnalog to digital converters reference12GNDAAnalog ground13AVDDOutput of the analog voltage regulator. Connect a capacitor to GNDA14VINChip supply input. Connect a capacitor to GNDP15NCNot connected16NCNot connected17ISPINPositive connection of the input current sense amplifier18ISNINNegative connection of the input current sense amplifier19HB1Bootstrap supply 1. Connect a capacitor between this pin and HS120HG1Output of the high side driver 121HS1Connect to the source of the high side 1 MOS22LG1Output of the low side driver 123GNDPPower ground24LG2Output of the low side driver 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7                                                      | SYNC      | Configurable input or output synchronization pin (if not used shall be configured as input and shall be grounded) |  |  |  |  |  |

| 10GNDDDigital ground11ADCREFAnalog to digital converters reference12GNDAAnalog ground13AVDDOutput of the analog voltage regulator. Connect a capacitor to GNDA14VINChip supply input. Connect a capacitor to GNDP15NCNot connected16NCNot connected17ISPINPositive connection of the input current sense amplifier18ISNINNegative connection of the input current sense amplifier19HB1Bootstrap supply 1. Connect a capacitor between this pin and HS120HG1Output of the high side driver 121HS1Connect to the source of the high side 1 MOS22LG1Output of the low side driver 123GNDPPower ground24LG2Output of the low side driver 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8                                                      | VDD_IO    | Digital interface supply pin                                                                                      |  |  |  |  |  |

| 11ADCREFAnalog to digital converters reference12GNDAAnalog ground13AVDDOutput of the analog voltage regulator. Connect a capacitor to GNDA14VINChip supply input. Connect a capacitor to GNDP15NCNot connected16NCNot connected17ISPINPositive connection of the input current sense amplifier18ISNINNegative connection of the input current sense amplifier19HB1Bootstrap supply 1. Connect a capacitor between this pin and HS120HG1Output of the high side driver 121HS1Connect to the source of the high side 1 MOS22LG1Output of the low side driver 123GNDPPower ground24LG2Output of the low side driver 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9                                                      | DVDD      | Output of the digital voltage regulator. Connect a capacitor to GNDD                                              |  |  |  |  |  |

| 12GNDAAnalog ground13AVDDOutput of the analog voltage regulator. Connect a capacitor to GNDA14VINChip supply input. Connect a capacitor to GNDP15NCNot connected16NCNot connected17ISPINPositive connection of the input current sense amplifier18ISNINNegative connection of the input current sense amplifier19HB1Bootstrap supply 1. Connect a capacitor between this pin and HS120HG1Output of the high side driver 121HS1Connect to the source of the high side 1 MOS22LG1Output of the low side driver 123GNDPPower ground24LG2Output of the low side driver 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10                                                     | GNDD      | Digital ground                                                                                                    |  |  |  |  |  |

| 13AVDDOutput of the analog voltage regulator. Connect a capacitor to GNDA14VINChip supply input. Connect a capacitor to GNDP15NCNot connected16NCNot connected17ISPINPositive connection of the input current sense amplifier18ISNINNegative connection of the input current sense amplifier19HB1Bootstrap supply 1. Connect a capacitor between this pin and HS120HG1Output of the high side driver 121HS1Connect to the source of the high side 1 MOS22LG1Output of the low side driver 123GNDPPower ground24LG2Output of the low side driver 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11                                                     | ADCREF    | Analog to digital converters reference                                                                            |  |  |  |  |  |

| 14VINChip supply input. Connect a capacitor to GNDP15NCNot connected16NCNot connected17ISPINPositive connection of the input current sense amplifier18ISNINNegative connection of the input current sense amplifier19HB1Bootstrap supply 1. Connect a capacitor between this pin and HS120HG1Output of the high side driver 121HS1Connect to the source of the high side 1 MOS22LG1Output of the low side driver 123GNDPPower ground24LG2Output of the low side driver 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12                                                     | GNDA      | Analog ground                                                                                                     |  |  |  |  |  |

| 15NCNot connected16NCNot connected17ISPINPositive connection of the input current sense amplifier18ISNINNegative connection of the input current sense amplifier19HB1Bootstrap supply 1. Connect a capacitor between this pin and HS120HG1Output of the high side driver 121HS1Connect to the source of the high side 1 MOS22LG1Output of the low side driver 123GNDPPower ground24LG2Output of the low side driver 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13                                                     | AVDD      | Output of the analog voltage regulator. Connect a capacitor to GNDA                                               |  |  |  |  |  |

| 16NCNot connected17ISPINPositive connection of the input current sense amplifier18ISNINNegative connection of the input current sense amplifier19HB1Bootstrap supply 1. Connect a capacitor between this pin and HS120HG1Output of the high side driver 121HS1Connect to the source of the high side 1 MOS22LG1Output of the low side driver 123GNDPPower ground24LG2Output of the low side driver 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14                                                     | VIN       | Chip supply input. Connect a capacitor to GNDP                                                                    |  |  |  |  |  |

| 17ISPINPositive connection of the input current sense amplifier18ISNINNegative connection of the input current sense amplifier19HB1Bootstrap supply 1. Connect a capacitor between this pin and HS120HG1Output of the high side driver 121HS1Connect to the source of the high side 1 MOS22LG1Output of the low side driver 123GNDPPower ground24LG2Output of the low side driver 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15                                                     | NC        | Not connected                                                                                                     |  |  |  |  |  |

| 18ISNINNegative connection of the input current sense amplifier19HB1Bootstrap supply 1. Connect a capacitor between this pin and HS120HG1Output of the high side driver 121HS1Connect to the source of the high side 1 MOS22LG1Output of the low side driver 123GNDPPower ground24LG2Output of the low side driver 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16                                                     | NC        | Not connected                                                                                                     |  |  |  |  |  |

| 19HB1Bootstrap supply 1. Connect a capacitor between this pin and HS120HG1Output of the high side driver 121HS1Connect to the source of the high side 1 MOS22LG1Output of the low side driver 123GNDPPower ground24LG2Output of the low side driver 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17                                                     | ISPIN     | Positive connection of the input current sense amplifier                                                          |  |  |  |  |  |

| 20HG1Output of the high side driver 121HS1Connect to the source of the high side 1 MOS22LG1Output of the low side driver 123GNDPPower ground24LG2Output of the low side driver 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18                                                     | ISNIN     | Negative connection of the input current sense amplifier                                                          |  |  |  |  |  |

| 21HS1Connect to the source of the high side 1 MOS22LG1Output of the low side driver 123GNDPPower ground24LG2Output of the low side driver 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19                                                     | HB1       | Bootstrap supply 1. Connect a capacitor between this pin and HS1                                                  |  |  |  |  |  |

| 22     LG1     Output of the low side driver 1       23     GNDP     Power ground       24     LG2     Output of the low side driver 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20                                                     | HG1       | Output of the high side driver 1                                                                                  |  |  |  |  |  |

| 23     GNDP     Power ground       24     LG2     Output of the low side driver 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 21                                                     | HS1       | Connect to the source of the high side 1 MOS                                                                      |  |  |  |  |  |

| 24         LG2         Output of the low side driver 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22                                                     | LG1       | Output of the low side driver 1                                                                                   |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23                                                     | GNDP      | Power ground                                                                                                      |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24                                                     | LG2       | Output of the low side driver 2                                                                                   |  |  |  |  |  |

| 25   VDD   Output of the internal regulator. Connect a capacitor to GNDP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25                                                     | VDD       | Output of the internal regulator. Connect a capacitor to GNDP                                                     |  |  |  |  |  |

| 26 HS2 Connect to the source of the high side 2 MOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 26                                                     | HS2       | Connect to the source of the high side 2 MOS                                                                      |  |  |  |  |  |

| 27 HG2 Output of the high side driver 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27                                                     | HG2       | Output of the high side driver 2                                                                                  |  |  |  |  |  |

| 28 HB2 Bootstrap supply 2. Connect a capacitor between this pin and HS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 28                                                     | HB2       | Bootstrap supply 2. Connect a capacitor between this pin and HS2                                                  |  |  |  |  |  |

| 29 VOUT Output voltage sense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                     | VOUT      | Output voltage sense                                                                                              |  |  |  |  |  |

| 30 VOUT_REF Output voltage reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30                                                     | VOUT_REF  | Output voltage reference                                                                                          |  |  |  |  |  |

| 31 ISNOUT Negative connection of the output current sense amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 31                                                     | ISNOUT    | Negative connection of the output current sense amplifier                                                         |  |  |  |  |  |

| 32 ISPOUT Positive connection of the output current sense amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 32                                                     | ISPOUT    | Positive connection of the output current sense amplifier                                                         |  |  |  |  |  |

| EP EP Exposed Thermal Pad: Heat slug, general device ground (shall be grounded)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | EP                                                     | EP        | Exposed Thermal Pad: Heat slug, general device ground (shall be grounded)                                         |  |  |  |  |  |

TABLE 1: MCP19061 PINOUT DESCRIPTION (SUMMARY)

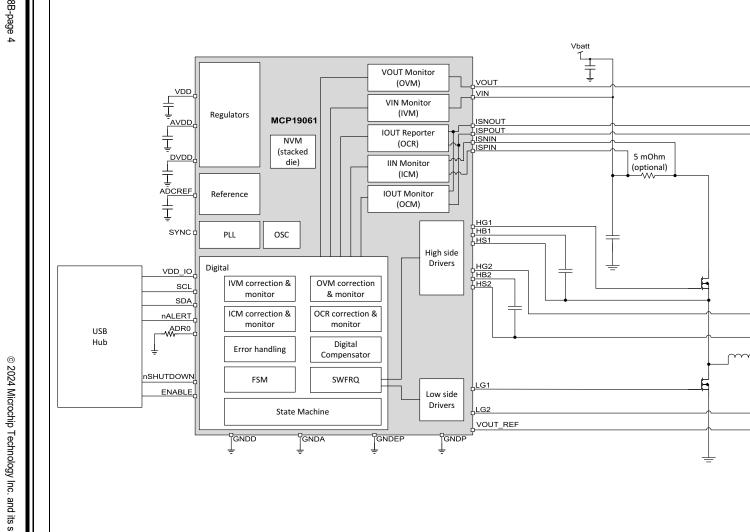

### MCP19061 Four Switch Buck Boost Block Diagram

vвus \_\_\_\_1

5 mOhm

÷

-~~~-

-

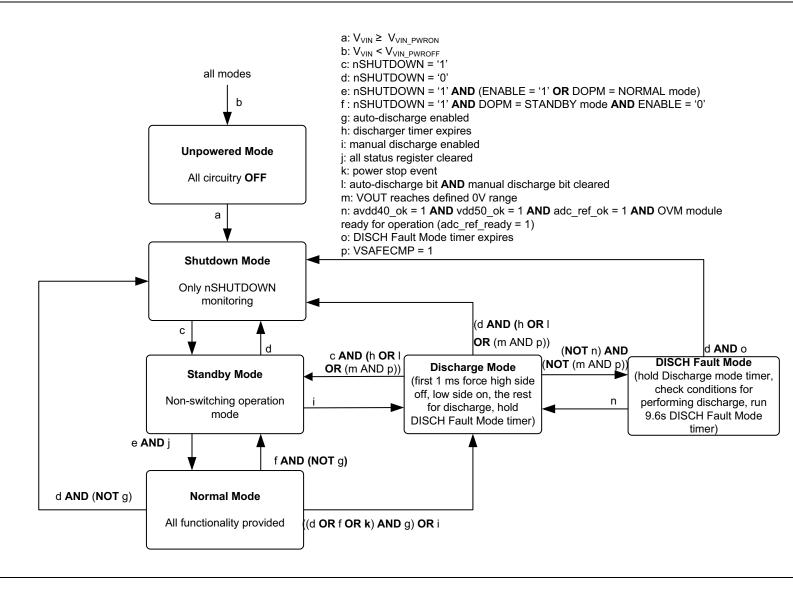

#### MCP19061 Mode Control

MCP19061

### **Table of Contents**

| Features                       | 1  |

|--------------------------------|----|

| 1.0 Pin Description            | 7  |

| 2.0 Functional Description     | 9  |

| 3.0 Electrical Characteristics | 11 |

| 4.0 Typical Performance Curves | 17 |

| 5.0 Configuring the MCP19061   |    |

| 6.0 Register Organization      | 20 |

| 7.0 Packaging Information      | 74 |

| Appendix A: Revision History   | 79 |

| Product Identification System  | 81 |

| Worldwide Sales and Service    | 84 |

## 1.0 **PIN DESCRIPTION**

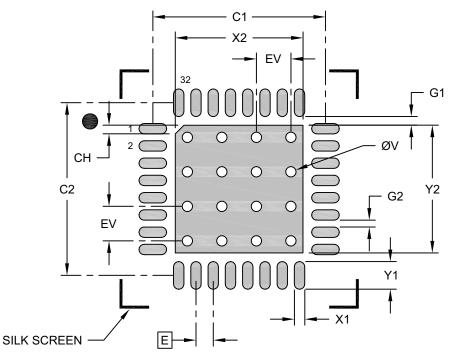

The description of pins for the 32-Lead VQFN package (summary) is listed in Table 1. The location of the pins and pad are shown in the Pin Diagram. A detailed pin description can be found below.

#### 1.1 Detailed Pin Functional Description

#### 1.1.1 nSHUTDOWN PIN

nSHUTDOWN pin forces the device in low power shutdown mode when pulled down.

#### 1.1.2 ENABLE PIN

ENABLE pin starts the power train when pulled high.

#### 1.1.3 ADR0 PIN

ADR0 pin sets the I2C address of the device. Connect a resistor to GND.

#### 1.1.4 SCL PIN

SCL pin is the clock of the I2C bus.

#### 1.1.5 SDA PIN

SCL pin is the data of the I2C bus.

#### 1.1.6 nALERT PIN

nALERT pin is an open drain pin. It is pulled low when an enabled internal event is detected.

#### 1.1.7 SYNC PIN

SYNC pin, when enabled, is used to synchronize the switching frequency and phase of multiple devices. It may be configured as input or output.

#### 1.1.8 VDD\_IO PIN

VDD\_IO is the digital interface supply pin. The voltage on this pin sets the logic levels on all digital pins. Connect a capacitor between this pin and the GNDD.

#### 1.1.9 DVDD PIN

DVDD is the output of the digital voltage regulator. Connect a capacitor to GNDD.

#### 1.1.10 GNDD PIN

GNDD is the digital ground connection pin.

This pin should be connected to the exposed pad on the bottom of the package.

#### 1.1.11 ADCREF PIN

ADCREF is the output of the ADC reference. Connect a capacitor to GNDA.

#### 1.1.12 GNDA PIN

GNDA is the small signal ground connection pin.

This pin should be connected to the exposed pad on the bottom of the package.

#### 1.1.13 AVDD PIN

AVDD is the output of the analog voltage regulator. Connect a capacitor to GNDA.

1.1.14 VIN PIN

Input power connection pin of the device. It is recommended that capacitance be placed between this pin and the GND pin of the device.

1.1.15 NC PIN

Connect to GND.

1.1.16 NC PIN

Connect to GND.

1.1.17 ISPIN PIN

The noninverting input to internal input current-sense amplifier, typically used to differentially remote-sense the input current on a high side shunt.

#### 1.1.18 ISNIN PIN

The inverting input to internal input current-sense amplifier, typically used to differentially remote-sense the input current on a high side shunt.

#### 1.1.19 HB1 PIN

Connect the bootstrap capacitor between this pin and the HS1 pin. The PCB trace connecting the bootstrap capacitor must be of minimal length and appropriate width to handle the high-peak drive currents and fast voltage transitions.

#### 1.1.20 HG1 PIN

Connect the gate of the high-side 1 MOSFET to this pin. The PCB trace connecting HG1 to the gate must be of minimal length and appropriate width to handle the high-peak drive currents and fast voltage transitions.

#### 1.1.21 HS1 PIN

Connect the source of the high-side 1 MOSFET to this pin. The PCB trace connecting HS1 to the gate must be of minimal length and appropriate width to handle the high-peak drive currents and fast voltage transitions.

#### 1.1.22 LG1 PIN

Connect the gate of the low-side 1 MOSFET to this pin. The PCB trace connecting LG1 to the gate must be of minimal length and appropriate width to handle the high-peak drive currents and fast voltage transitions.

#### 1.1.23 GNDP PIN

Connect all large-signal level ground returns to GNDP. These large-signal level ground traces should have a small loop area and minimal length to prevent coupling of switching noise to sensitive traces.

This pin should be connected to the exposed pad on the bottom of the package.

#### 1.1.24 LG2 PIN

Connect the gate of the low-side 2 MOSFET to this pin. The PCB trace connecting LG2 to the gate must be of minimal length and appropriate width to handle the high-peak drive currents and fast voltage transitions.

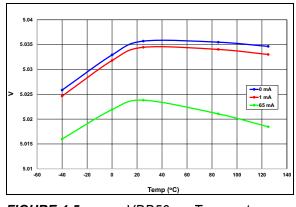

#### 1.1.25 VDD PIN

The output of the internal +5.0V regulator is connected to this pin. It is recommended that a 1.0  $\mu$ F minimum/ 10  $\mu$ F maximum bypass capacitor be connected between this pin and the GND pin of the device. The bypass capacitor should be physically placed close to the device.

#### 1.1.26 HS2 PIN

Connect the source of the high-side 2 MOSFET to this pin. The PCB trace connecting HS2 to the source must be of minimal length and appropriate width to handle the high-peak drive currents and fast voltage transitions.

#### 1.1.27 HG2 PIN

Connect the gate of the high-side 2 MOSFET to this pin. The PCB trace connecting HG2 to the gate must be of minimal length and appropriate width to handle the high-peak drive currents and fast voltage transitions.

#### 1.1.28 HB2 PIN

Connect the bootstrap capacitor between this pin and the HS2 pin. The PCB trace connecting the bootstrap capacitor must be of minimal length and appropriate width to handle the high-peak drive currents and fast voltage transitions.

#### 1.1.29 VOUT PIN

Output voltage sensing pin. Connect this pin to the output of the power supply.

#### 1.1.30 VOUT\_REF PIN

Output remote ground sensing pin. Connect this pin to the load GND.

#### 1.1.31 ISNOUT PIN

The inverting input to the internal output current-sense amplifier, typically used to differentially remote-sense the output current on output high side shunt.

| Caution: | Do not filter this pin voltage, results may |

|----------|---------------------------------------------|

|          | be unpredictable!                           |

#### 1.1.32 ISPOUT PIN

The noninverting input to the internal output current-sense amplifier, typically used to differentially remote-sense the output current on output high side shunt.

| Caution: | Do not filter this pin voltage, results may |

|----------|---------------------------------------------|

|          | be unpredictable!                           |

#### 1.1.33 EXPOSED PAD (EP)

The exposed pad is used for GND connection and thermal dissipation. Connect the exposed pad to GND.

## 2.0 FUNCTIONAL DESCRIPTION

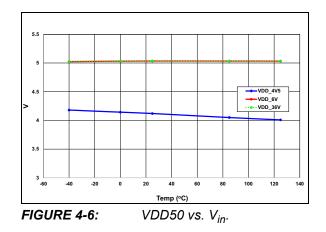

### 2.1 Linear Regulators

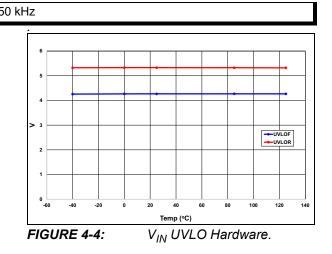

The operating input voltage for the MCP19061 ranges from +4.5V to +36V. The internal 5V LDO provides bias voltage for integrated MOSFET drivers and also can be used to bias additional external circuitry. Care should be exercised to avoid LDO overload. The output of the LDO is monitored and specific fault is generated in case of malfunction.

The internal 4V regulator provides bias voltage for the analog circuitry. The internal 1.8V regulator provides bias voltage for the digital core.

The bits that monitor the functionality of the LDOs are located in STASYS register. For each regulator, a decoupling capacitor must be connected between output pin and ground (4.7  $\mu$ F/25V X7R ceramic capacitor).

### 2.2 ADCREF

An accurate reference voltage is internally provided for all voltage and current measurements and settings. A decoupling capacitor (recommended 1  $\mu$ F/25V X7R, ceramic) must be connected to the ADCREF output pin.

### 2.3 Output Drive Circuitry

The MCP19061 integrates two low side and two high side drivers used to drive 4 external N-Channel power MOSFETs in a 4 switch buck-boost configuration. The floating MOSFET gate is connected to the HGx pin. The source of this MOSFET is connected to HSx pin. The low side MOSFET gate is connected to LGx pin and the source is connected to GNDP. The output drivers dead time is set with the DT<4:0> bits in the SWFRQCON1 Register, Register 6-20.

#### 2.4 Current Sense

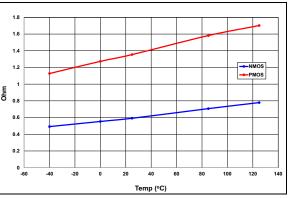

The input and output currents are differentially sensed by the MCP19061. The output current sense amplifier is optimized for 5 m $\Omega$  shunt resistors.

**Caution:** Do not insert differential or common mode filters in the input of the current sense amplifiers or unexpected behavior may occur. The traces connecting the CSA inputs with the shunts must be carefully differential routed to avoid noise coupling.

#### 2.5 Voltage Sense

The MCP19061 measures both input and output voltages with fast ADCs. The values may be reported via the  $I^2C$  and are used by the internal state machine to control and protect.

The input voltage is measured on the VIN pin.

The output voltage is differentially measured between the VOUT and the VOUT\_REF pins. It is recommended to route the VOUT and the VOUT\_REF pins differentially to the output connections and to insert an RC filter between. Use  $100\Omega$  series resistor and compute the capacitor to have the same RC as the output bulk capacitor/ESR:

$$C = \frac{Output Cap \times ESR}{100}$$

#### 2.6 Power Control Circuitry

The internal driver control of the MCP19061 is comprised of a digital control loop, four fast ADCs, several calibration circuits and several analog comparators.

The input and output voltages and currents are sampled by the four analog to digital converters. The digital converted values are corrected as offset and gain in digital blocks.

The corrected ADC values are compared to the target values by the digital modulator that generates the PWM signals accordingly.

The same corrected ADC values and several other digitized analog signals are used by the configurable digital protection circuit to alert the user and/or stop the power train if undesired events occur.

The control loop parameters are set in the following registers:

- BCKGPI Register 6-3 sets the buck control loop gain.

- BSTGPI Register 6-4 sets the boost control loop gain.

- SLOPCOMP Register 6-6 sets the factor for calculating the slope compensation value.

- SYSCAP Register 6-5 must be set in accordance to the used output capacitance and switching frequency.

- LC Register 6-23 must be set in accordance to the used inductor value.

Caution: Loop control registers can be written only when the power train is stopped!

Caution: Not using the recommended values for the loop parameters may lead to unpredictable results!

### 2.7 Output Regulation

The MCP19061 regulates both output voltage and output current. If both are enabled, the mode transition is seamless.

Output voltage set point must be written in the VREF<11:0> bits in the VREF Register 6-18.

Output current set point must be written in the IREF<11:0> in the IREF Register 6-19.

Output current regulation may be disabled by setting low the IREGEN bit in the COMPMODE Register 6-32.

### 2.8 PLL Control

The MCP19061 is internally clocked by a PLL (Phase Lock Loop) multiplied ring oscillator.

The source of this clock may be an internal 1.8 MHz oscillator or the SYNC pin. The selection is made in the PLLCON Register 6-35.

The ring oscillator optimum frequency is 36 MHz. The multiplication factor shall be set with the PLLPR bits in the PLLCON Register 6-35.

The recommended value of the ring oscillator is 36 MHz, therefore the PLLPR value shall be set to 0x4F, if the internal clock is selected, or to (36 MHz/SYNC frequency - 1), if external synchronization is needed.

The PLLCON Register 6-35 cannot be modified if any function needing the 36 MHz clock is enabled: power switching, discharge, ADC reading.

#### 2.9 PWM Frequency

The switching frequency of the MCP19061 can be set in the SWFREQ2 Register 6-21.

To reduce EMI, the frequency may be user-selectable dithered. Dithering may be enabled by setting the DITHER bit in the SWFRQCON1 Register 6-20 and configured in the DITHER Register 6-22.

### 2.10 Synchronization

MCP19061 may output it's PWM frequency on the SYNC pin to allow the synchronization of other devices. To enable the sync function and set its direction the AUTORVB, CLKOUTEN and CLKSRC bits in the PLLCON Register 6-35 must be set.

MCP19061 may also synchronize it's PWM frequency to an external 300 kHz to 500 kHz input on SYNC pin. The PWM signal may have a programmable phase. The requested values to set the frequency parameters must be written in the PLLCON Register 6-35, SWFRQCON1 Register 6-20 and SWFRQCON2 Register 6-21.

Caution: All frequency related registers can be written only when the power train is stopped!

#### 2.11 Temperature Management

To protect the MCP19061 from overtemperature conditions, a 150°C (min.) junction temperature thermal shutdown has been implemented. When the junction temperature reaches this limit, the device disables the output drivers. When the junction temperature is reduced by 20°C (typ.), output drive switching can be re-enabled after clearing the corresponding overtemperature flag.

#### 2.12 USB Specific Circuits

#### 2.12.1 OUTPUT DISCHARGE

The output discharge circuit will remove the charge stored in the output capacitor at each power stop. The output voltage of the power supply is reduced to VSafe0 in less than 600 ms. Once any of the above conditions is met the discharge stops. The function is automatic, occurring each time the device is disabled or shutdown if the AUTODSCH bit in the MODECON Register 6-34 is set. A discharge may be initiated at any moment, if the output power is stopped, setting high the MANUDSCH bit in the MODECON Register 6-34. If the discharge did not succeed to drop the output voltage below VSafe0 in 600 ms the DISCHFAIL flag in the STASYS Register 6-41 is set.

#### 2.12.2 OVERLOAD DETECTION

The MCP19061 detects an overload condition in accordance with the USB-PD and Apple peripheral requirements allowing high peak currents to pass for a given time. The overload profile and maximum current can be set in the USBOLD Register 6-27. The overload detection will set the OCROC in the STABB Register 6-42.

#### 2.12.3 SHORT CIRCUIT DETECTION

In accordance with the USB-PD requirements, MCP19061 detects short circuit by entering in the current regulation mode and checking if the output voltage dropped bellow 2V. The detection of the short will set the OCRSC flag in the STABB Register 6-42.

#### 2.12.4 OUTPUT VOLTAGE RISE/FALL WITH CONTROLLED SPEED

MCP19061 controls the speed of all the changes in the output voltage. The maximum speed is  $30 \text{ mV/}\mu\text{s}$  in accordance with USB-PD, but can be set lower with the VRAMP<3:0> from the VREF Register 6-18.

#### 2.12.5 OUTPUT RESISTANCE IN STAND-BY OR SHUTDOWN

If the power train is stopped, the impedance of the MCP19061 at the VOUT connections exceeds 200K, thus allowing the detection of released line without needing a disconnect switch.

## 3.0 ELECTRICAL CHARACTERISTICS

## 3.1 ABSOLUTE MAXIMUM RATINGS<sup>†</sup>

| V <sub>VIN</sub> , V <sub>ISPIN</sub> , V <sub>ISNIN</sub> , V <sub>HS1</sub> (DC)<br>V <sub>HG1</sub> , V <sub>HB1</sub> (DC)<br>V <sub>VOUT</sub> , V <sub>ISPOUT</sub> , V <sub>ISNOUT</sub> , V <sub>HS2</sub> (DC)<br>V <sub>HB2</sub> , V <sub>HG2</sub> (DC)<br>V <sub>LG1</sub> , V <sub>LG2</sub> (DC)<br>V <sub>HGx</sub> -V <sub>HSx</sub> , V <sub>HBx</sub> -V <sub>HSx</sub><br>V <sub>DVDD</sub> (DC)<br>V <sub>VDD_IO</sub> , V <sub>VDD</sub> , V <sub>AVDD</sub> , V <sub>ADCREF</sub> , (DC)<br>V <sub>ISPIN</sub> -V <sub>VIN</sub> (DC)<br>V <sub>ISNIN</sub> -V <sub>VIN</sub> (DC)<br>V <sub>ISNIN</sub> -V <sub>VIN</sub> , (Transient, <100 nsec) | 0.3V to +40V<br>0.3V to +45.5V<br>0.3V to +5.5V<br>0.3V to +5.5V<br>0.3V to +5.5V<br>0.3V to +5.5V<br>2V to +2V<br>36.7V to +5.5V<br>42V to +5.5V |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |

| V <sub>ISPIN</sub> -V <sub>VIN</sub> (DC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2V to +2V                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |

| V <sub>ISNIN</sub> -V <sub>VIN</sub> ,(Transient, <100 nsec)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 42V to +5.5V                                                                                                                                      |

| V <sub>ISPOUT</sub> -V <sub>VOUT</sub> , <sub>VISNOUT</sub> -V <sub>VOUT</sub> ,(DC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                   |