# SGM61412 1.2MHz, 1.2A, 42V Synchronous Buck Converter

#### GENERAL DESCRIPTION

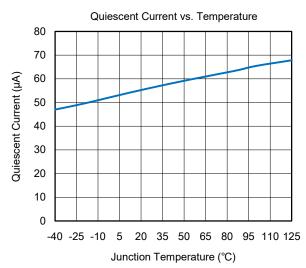

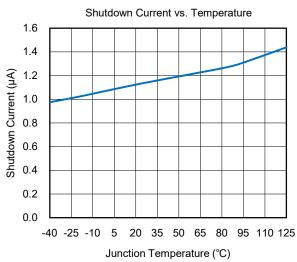

The SGM61412 is a high frequency, synchronous Buck converter with integrated switches. It can deliver up to 1.2A to the output over a wide input voltage range of 4.5V to 42V. It is suitable for various industrial applications with high input voltage or for power conditioning from unregulated sources. Moreover, the low 55µA quiescent current and ultra-low shutdown current of only 1.2µA make it a suitable choice for battery-powered applications.

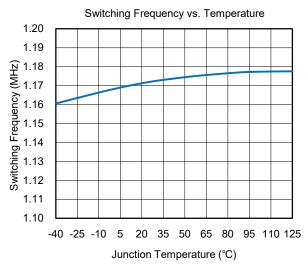

SGM61412 features high efficiency over a wide load range achieved by scaling down the switching frequency at light load condition to reduce switching and gate driving losses. Other features include internal compensation, internal monotonic soft-start even with pre-biased output and fast loop response due to the peak-current mode controller. Switching at 1.2MHz, the SGM61412 can prevent EMI noise problems, such as the ones found in AM radio, ADSL and PLC applications.

Protection features include current limit and short-circuit protection, thermal shutdown with auto recovery and output over-voltage protection. Frequency fold-back helps prevent inductor current runaway during startup.

The SGM61412 is available in a Green TSOT-23-6 package. It operates over a wide ambient temperature range of -40°C to +125°C.

#### **FEATURES**

- Wide 4.5V to 42V Input Voltage Range

- Current Output up to 1.2A

- 1.2MHz Switching Frequency

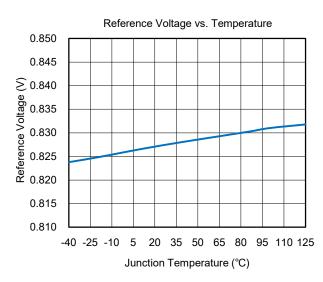

- 0.83V Internal Reference

- SGM61412A:PSM and PWM Mode

- SGM61412B: PFM and PWM Mode

- Low Quiescent Current: 55μA (TYP)

- Ultra-Low Shutdown Current: 1.2µA (TYP)

- 0.83V to 20V Adjustable Output Voltage

- Internal Compensation and Soft-Start

- Precision Enable Function with UVLO Setting

- Monotonic Startup with Pre-biased Output

- Thermal Shutdown Protection

- Available in a Green TSOT-23-6 Package

- -40°C to +125°C Operating Temperature Range

#### **APPLICATIONS**

High Voltage Power Conversions Industrial Power Systems Distributed Power Systems Battery Powered Systems Power Meters

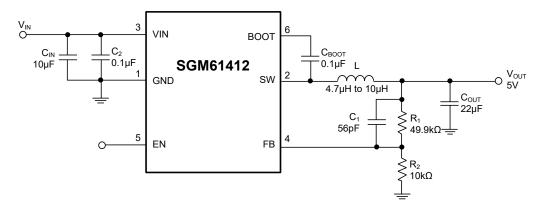

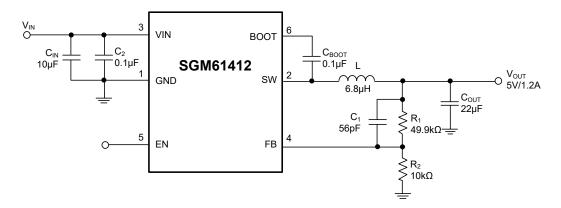

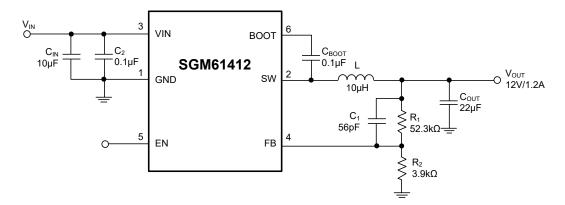

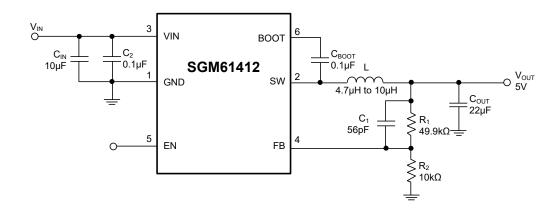

#### TYPICAL APPLICATION

Figure 1. Typical Application Circuit

#### PACKAGE/ORDERING INFORMATION

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING | PACKING<br>OPTION   |

|-----------|------------------------|-----------------------------------|--------------------|--------------------|---------------------|

| SGM61412A | TSOT-23-6              | -40°C to +125°C                   | SGM61412AXTN6G/TR  | CN1XX              | Tape and Reel, 3000 |

| SGM61412B | TSOT-23-6              | -40°C to +125°C                   | SGM61412BXTN6G/TR  | CN2XX              | Tape and Reel, 3000 |

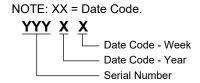

#### MARKING INFORMATION

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| VIN to GND                        | 0.3V to 45V                    |

|-----------------------------------|--------------------------------|

| EN to GND                         | 0.3V to V <sub>IN</sub> + 0.3V |

| FB to GND                         | 0.3V to 5.5V                   |

| SW to GND                         | 0.3V to V <sub>IN</sub> + 0.3V |

| BOOT to SW                        | 0.3V to 5.5V                   |

| Package Thermal Resistance        |                                |

| TSOT-23-6, θ <sub>JA</sub>        | 132°C/W                        |

| Junction Temperature              | +150°C                         |

| Storage Temperature Range         | 65°C to +150°C                 |

| Lead Temperature (Soldering, 10s) | +260°C                         |

| ESD Susceptibility                |                                |

| HBM                               | 2000V                          |

| CDM                               | 1000V                          |

#### RECOMMENDED OPERATING CONDITIONS

| Supply Input Voltage Range4.             | 5V to 42V |

|------------------------------------------|-----------|

| Operating Junction Temperature Range40°C | to +125℃  |

| Operating Ambient Temperature Range40°C  | to +125°C |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

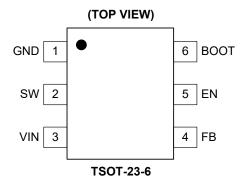

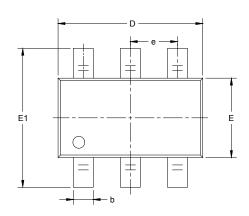

# **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GND  | Ground Pin. It is the reference for input and the regulated output voltages. Special layout considerations are required.                                                                                                                                                                                                                                                                                                                           |

| 2   | SW   | Switching Node Output. Switching node of the internal power converter and should be connect to the output inductor and bootstrap capacitor. This node should be kept small on the PCB to minimize capacitive coupling, noise coupling and radiation.                                                                                                                                                                                               |

| 3   | VIN  | Power Supply Input Pin. This pin is connected to the input supply voltage and powers the internal control circuitry. VIN voltage is monitored by a UVLO lockout comparator. VIN is also connected to the drain of the converter high-side switch. Due to power switching, this pin has high di/dt transition edges and must be decoupled to the GND by input capacitors as close as possible to the GND pin to minimize the parasitic inductances. |

| 4   | FB   | Feedback Input. Feedback pin for programming the output voltage. The SGM61412 regulates the FB pin to 0.83V. Connect the midpoint of the feedback resistor divider.                                                                                                                                                                                                                                                                                |

| 5   | EN   | Active High Enable Input. Internal pull-up current source. Pull below 0.9V to disable the device. Float to enable. Adjust the input under-voltage lockout with a resistor divider.                                                                                                                                                                                                                                                                 |

| 6   | воот | Bootstrap Input. Bootstrap pin is used to provide a drive voltage, higher than the input voltage, to the high-side power switch. Place a $0.1\mu F$ Boost capacitor ( $C_{BOOT}$ ) as close as possible to the IC between this pin and SW pin.                                                                                                                                                                                                     |

# **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 24V, T_J = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ typical values are at } T_J = +25^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETE                   | R                | SYMBOL                | CONDITIONS                                                                 | MIN   | TYP   | MAX   | UNITS |  |

|----------------------------|------------------|-----------------------|----------------------------------------------------------------------------|-------|-------|-------|-------|--|

| Supply Input Voltage       |                  | V <sub>IN</sub>       |                                                                            | 4.5   |       | 42    | V     |  |

| Under-Voltage Lockout Thre | shold            | V <sub>UVLO</sub>     |                                                                            | 4.00  | 4.25  | 4.50  | V     |  |

| Under-Voltage Lockout Thre | shold Hysteresis | V <sub>UVLO_HYS</sub> |                                                                            |       | 320   |       | mV    |  |

|                            | Shutdown         |                       | V <sub>EN/UV</sub> = 0V                                                    |       | 1.2   | 2.0   |       |  |

| VIN Quiescent Current      | Sleep Mode       | ΙQ                    | V <sub>EN/UV</sub> = 2V, Non-switching, V <sub>IN</sub> ≤ 36V<br>SGM61412A |       | 55    | 85    | μΑ    |  |

|                            | Sleep Wode       |                       | V <sub>EN/UV</sub> = 2V, Non-switching, V <sub>IN</sub> ≤ 36V<br>SGM61412B |       | 1.95  | 2.8   | mA    |  |

| Feedback Reference Voltag  | е                | $V_{FB}$              |                                                                            | 0.805 | 0.830 | 0.855 | V     |  |

| Feedback Pin Input Current |                  | I <sub>FB</sub>       | V <sub>FB</sub> = 1V                                                       |       | 0.1   | 1     | μΑ    |  |

| Minimum High-side Switch ( | On-Time          | t <sub>ON_MIN</sub>   | I <sub>LOAD</sub> = 1A                                                     |       | 100   |       | ns    |  |

| Minimum High-side Switch ( | Off-Time         | toff_min              | I <sub>LOAD</sub> = 1A                                                     |       | 120   |       | ns    |  |

| Switching Frequency        |                  | f <sub>SW</sub>       |                                                                            | 0.85  | 1.2   | 1.55  | MHz   |  |

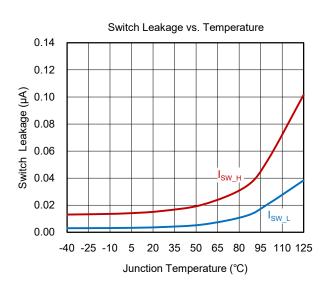

| Switch Lookage Current     |                  | I <sub>SW_H</sub>     | V <sub>SW</sub> = 42V                                                      |       | 0.1   | 1     | μА    |  |

| Switch Leakage Current     |                  | I <sub>SW_L</sub>     | V <sub>SW</sub> = 0V                                                       |       | 0.1   | 1     |       |  |

| High-side NMOS Current Lin | nit              | I <sub>LIM</sub>      | T <sub>J</sub> = +25°C                                                     | 1.6   | 2.0   | 2.4   | Α     |  |

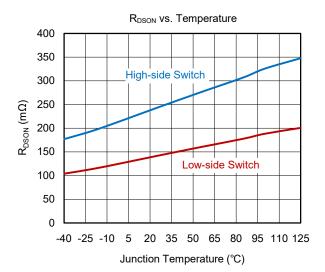

| High-side NMOS On-Resist   | ance             | Б                     | I <sub>LOAD</sub> = 0.1A                                                   |       | 230   | 410   | mΩ    |  |

| Low-side NMOS On-Resista   | ince             | R <sub>DSON</sub>     | I <sub>LOAD</sub> = 0.1A                                                   |       | 130   | 230   | mΩ    |  |

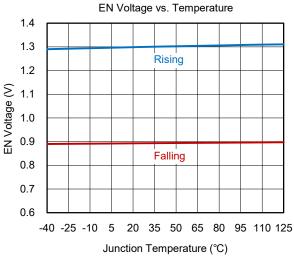

| EN Input High Voltage      |                  | V <sub>IH</sub>       | V <sub>EN</sub> Rising                                                     | 1.2   | 1.3   | 1.4   | V     |  |

| EN Input Low Voltage       |                  | V <sub>IL</sub>       | V <sub>EN</sub> Falling                                                    | 0.8   | 0.9   | 1.0   | V     |  |

| EN Threshold, Hysteresis   |                  | V <sub>EN_HYS</sub>   |                                                                            |       | 400   |       | mV    |  |

| Enable Leakage Current     |                  |                       | V <sub>EN</sub> = 42V                                                      |       | 0.1   | 1     | μА    |  |

|                            |                  | I <sub>EN</sub>       | V <sub>EN</sub> = 0V                                                       | -1    | -0.4  |       |       |  |

| Thermal Shutdown           |                  | T <sub>SHDN</sub>     |                                                                            |       | 155   |       | °C    |  |

| Thermal Shutdown Hysteres  | sis              | T <sub>HYS</sub>      |                                                                            |       | 30    |       | °C    |  |

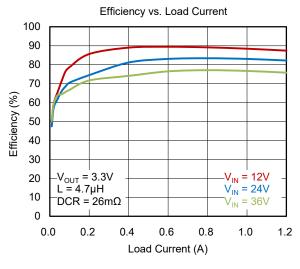

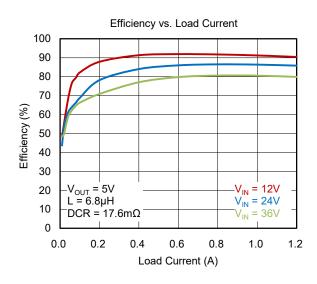

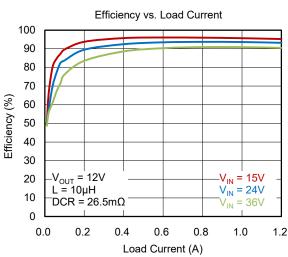

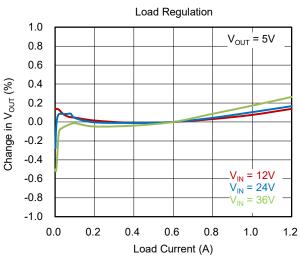

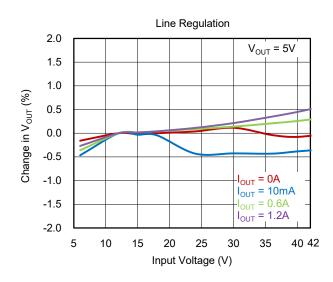

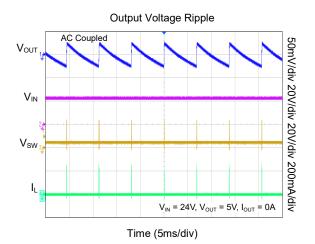

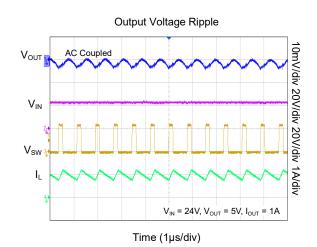

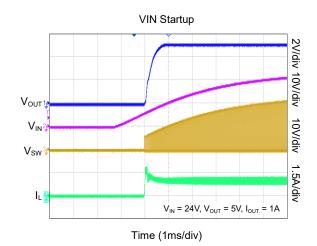

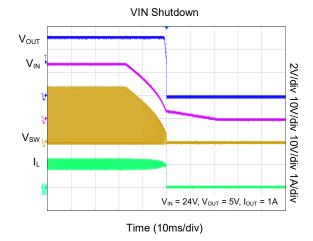

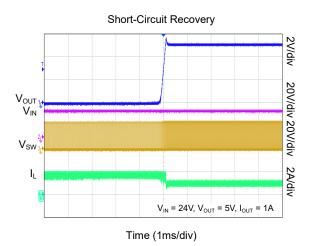

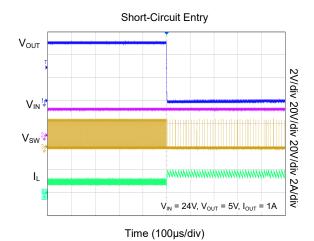

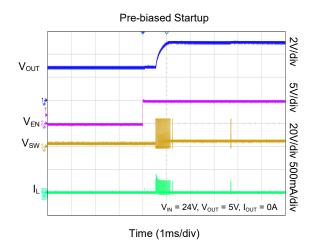

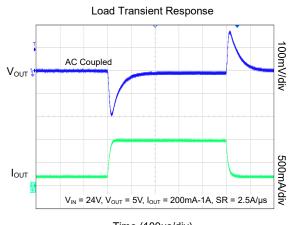

#### TYPICAL PERFORMANCE CHARACTERISTICS

Time (100µs/div)

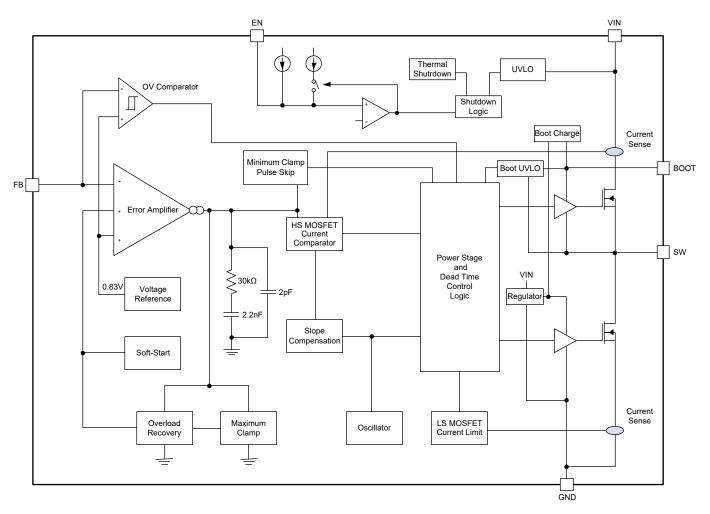

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Block Diagram

#### **DETAILED DESCRIPTION**

#### Overview

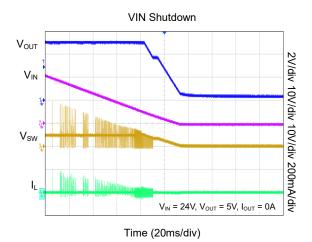

The SGM61412 is an internally compensated wide input range current mode controlled synchronous step-down converter. It is designed for high reliability and is particularly suitable for power conditioning from unregulated sources or battery-powered applications that need low sleep and shutdown currents. It also features a power-save mode in which operating frequency is adaptively reduced under light load condition to reduce switching and gate losses and keep high efficiency. At no load and with switching stopped, the total operating current is approximately 55µA. If the device is disabled, the total consumption is typically 1.2µA.

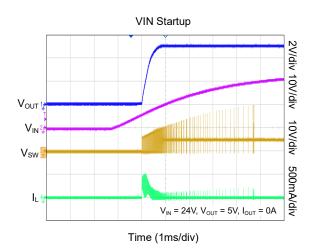

Figure 2 shows the functional block diagram of the SGM61412. The two integrated MOSFET switches of the power stage are both over-current protected and can provide up to 1.2A of continuous current for the load. Current limit of the switches also prevents inductor current runaway. The converter switches are optimized for high efficiency at low duty cycle.

At the beginning of each switching cycle, the high-side switch is turned on. This is the time that feedback voltage ( $V_{FB}$ ) is below the reference voltage ( $V_{REF}$ ) and power must be delivered to the output. After the on-period, the high-side switch is turned off and the low-side switch is turned on until the end of switching cycle. For reliable operation and preventing shoot through, a short dead time is always inserted between gate pulses of the converter complimentary switches. During dead time, both switch gates are kept off.

The device is designed for safe monotonic start-up even if the output is pre-biased.

If the junction temperature exceeds a maximum threshold ( $T_{SHDN}$ , typically +155°C), thermal shutdown protection will happen and switching will stop. The device will automatically recover with soft-start when the junction temperature drops back well below the trip point. This hysteresis is typically 30°C.

The SGM61412 has current limit on both the high-side and low-side MOSFET switches. When current limit is activated frequency fold-back is also activated. This occurs in the case of output overload or short circuit. Note that SGM61412 will continue to provide its maximum output current and will not shut down. In such a case, the junction temperature may rise rapidly and trigger thermal shutdown.

During initial power-up of the device (soft-start), current limit and frequency fold-back are activated to prevent inductor current runaway while the output capacitor is charging to the desired  $V_{\text{OUT}}$ .

#### **Peak-Current Mode (PWM Control)**

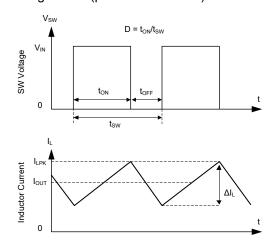

Figure 2 shows the functional block diagram and Figure 3 shows the switching node operating waveforms of the SGM61412. Switching node voltage is generated by controlling the duty cycles of the complementary high-side and low-side switches. The high-side duty cycle is used as control parameter of the Buck converter to regulate output voltage and is defined as:  $D = t_{ON}/t_{SW}$ , where  $t_{ON}$  is the high-side switch on-time and t<sub>SW</sub> is the switching period. When high-side switch is turned on, the SW pin voltage sharply rises towards V<sub>IN</sub>, and the inductor current (I<sub>L</sub>) starts ramping up with (V<sub>IN</sub> - V<sub>OUT</sub>)/L slope. When high-side switch is turned off, the low-side switch is turned on after a very short dead time to avoid shoot-through, and I<sub>L</sub> ramps down with -V<sub>OUT</sub>/L slope. In ideal case, the output voltage is proportional to the input voltage and duty cycle (D = V<sub>OUT</sub>/V<sub>IN</sub>) if component parasitics are ignored.

The SGM61412 employs fixed-frequency, peak-current mode control in continuous conduction mode (CCM) (when inductor minimum current is above zero). In light load condition (when the inductor current reaches zero) the SGM61412 will enter discontinuous conduction mode (DCM) and the control mode will change to shift-frequency, peak-current mode to reduce the switching frequency and the associated switching and gate driving losses (power-save mode).

Figure 3. Converter Switching Waveforms in CCM

# **DETAILED DESCRIPTION (continued)**

In CCM, SGM61412 operates at fixed-frequency using peak-current mode control scheme. The controller has an outer voltage feedback loop to get accurate DC voltage regulation. The output of the outer loop is fed to an inner peak-current control loop as reference command that adjusts the peak-current of the inductor. The inductor peak-current is sensed from the high-side switch and is compared to the peak-current reference to control the duty cycle. In other words, as soon as the inductor current reaches the reference peak-current determined by voltage loop, the high-side switch is turned off and the low-side switch is turned on after dead time.

The internally compensated voltage feedback loop allows for simpler design, fewer external components, and stable operation with almost any combination of output capacitors.

#### Power-Save Mode (SGM61412A Only)

The SGM61412A/B operate in PWM mode to provide lower ripple at heavy load. The SGM61412A operates in power-save mode (PSM) at light load to boost light load efficiency by reducing switching and gate drive losses. When the inductor peak-current is low and the internal  $V_{\text{COMP}}$  falls to the internal threshold, the device will enter PSM. After entering PSM for a delay time, some modules are shut down to minimum quiescent current. The high-side MOSFET will not switch until the output voltage falls for the internal  $V_{\text{COMP}}$  to rise above the internal threshold. Since the integrated current comparator catches the inductor peak-current only, the average load current entering PSM varies with the applications and external output filters.

#### Pulse Frequency Mode (SGM61412B Only)

As the load current decreases, the SGM61412B enters pulse frequency mode (PFM). When the inductor peak-current is low and the internal  $V_{\text{COMP}}$  falls to the internal threshold, the device will enter PFM. During PFM, when output feedback voltage  $V_{\text{FB}}$  falls below 0.83V typically, the device starts a PFM current pulse. The high-side MOSFET switch is turned on, and the inductor current ramps up. As the inductor peak-current rise for the current sense voltage  $V_{\text{SENSE}}$  reaches the internal threshold, the switch is turned off and the low-side MOSFET switch is turned on until the inductor current becomes zero. The converter effectively delivers a current to the output capacitor and the load.

The resulting PFM frequency mainly depends on the load current. The lighter the load, the slower the output voltage drops, and the lower switching frequency. Lower switching frequency reduces the switching and gate drive losses, and improves the efficiency significantly. The PFM is left and PWM mode entered in case the output current rise for the internal  $V_{\text{COMP}}$  to rise above the internal threshold.

# Floating Driver and Bootstrap Charging UVLO Protection

The high-side MOSFET driver is powered by a floating supply provided by an external bootstrap capacitor. The bootstrap capacitor is charged and regulated to about 5V by the dedicated internal bootstrap regulator. When the voltage between BOOT and SW nodes is below regulation, a PMOS pass transistor is turned on and connected VIN and BOOT pins internally, otherwise it will be turned off. The power supply for the floating driver has its own UVLO protection. The rising UVLO threshold is about 4.25V and with 320mV hysteresis; the falling threshold is about 3.93V. In case of UVLO, the reference voltage of the controller is reset to zero and after recovery a new soft-start process will start.

# Minimum High-side On/Off-Time and Frequency Fold-Back

The shortest duration for the high-side switch on-time  $(t_{ON\_MIN})$  is 100ns (TYP). For the off-time  $(t_{OFF\_MIN})$  the minimum value is 120ns (TYP). The duty cycle (or equivalently the  $V_{OUT}/V_{IN}$  ratio) range in CCM operation is limited by  $t_{ON\_MIN}$  and  $t_{OFF\_MIN}$  depending on the switching frequency. Note that at 1.2MHz the total cycle time is  $t_{SW}$  = 833ns.

The minimum and maximum duty cycles without frequency fold-back are given by Equations 1 and 2:

$$D_{MIN} = t_{ON MIN} \times f_{SW}$$

(1)

$$D_{MAX} = 1 - t_{OFF MIN} \times f_{SW}$$

(2)

For any given output voltage, the highest input voltage without frequency fold-back can be calculated from:

$$V_{IN\_MAX} = \frac{V_{OUT}}{f_{SW} \times f_{ON\ MIN}}$$

(3)

The minimum  $V_{IN}$  is estimated by:

$$V_{IN\_MIN} = \frac{V_{OUT}}{1 - f_{SW} \times t_{OFF\ MIN}}$$

(4)

# **DETAILED DESCRIPTION (continued)**

#### Input Voltage

The SGM61412 can operate efficiently for inputs as high as 42V. For CCM operation keeps duty cycle between 12% and 88%.

#### **Output Voltage**

The output voltage can be bucked to as low as the 0.83V reference voltage (V<sub>REF</sub>). As explained before, when the output voltage is set to 0.83V and there is no voltage divider, a minimum small load will be needed. An  $80k\Omega$  resistor to ground will prevent the output voltage floating up.

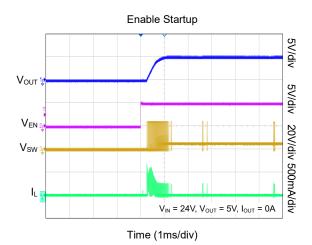

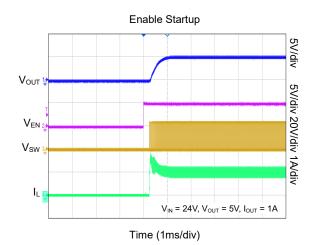

#### **Soft-Start**

The integrated soft-start circuit in SGM61412 limits the input inrush current right after power-up or enabling the device. Soft-start is implemented by slowly ramping up the reference voltage that in turn slowly ramps up the output voltage to its target regulation value.

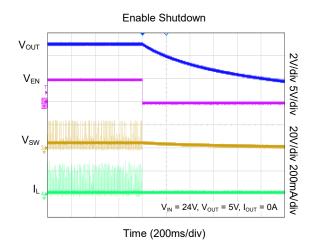

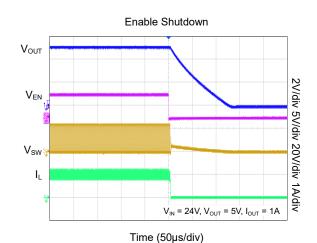

#### **Enable**

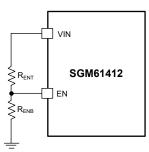

EN pin turns the SGM61412 operation in on or off condition. If an applied voltage is less than 0.9V, the device will shut down. If the voltage is more than 1.3V, the device will start the regulator. The simplest way to enable the device is to connect the EN pin to VIN pin via a resistor. This enables the SGM61412 to start up automatically when VIN is within the operating range.

Many applications will profit from the employment of an enable divider  $R_{\text{ENT}}$  and  $R_{\text{ENB}}$  (see Figure 4) to build an accurate system UVLO level for the converter. System UVLO can be used for supplies operating from utility power as well as battery power. This feature can be used for power supply sequencing which is required for proper power up of the system voltage rails. It can also be used as protection, such as preventing supply battery from depletion. Control of the enable input by logic signals may also be used for sequencing or protection.

Figure 4. System UVLO by Enable Divider

#### **Thermal Shutdown**

Thermal protection is designed to protect the die against overheating damage. If the junction temperature exceeds +155°C, the switching stops and the device shuts down. Automatic recovery with an internal soft-start will begin when the junction temperature drops below the +125°C falling threshold.

## TYPICAL APPLICATION CIRCUITS

Figure 5. 5V Output Typical Application Circuit for Power Meters

Figure 6. 12V Output Typical Application Circuit for Power Meters

#### APPLICATION INFORMATION

#### **External Components**

The following guides can be used to select external components.

| f <sub>SW</sub> (MHz) | V <sub>OUT</sub> (V) | R <sub>1</sub> (kΩ) | R <sub>2</sub> (kΩ) | L (µH) | Своот (µF) | C <sub>IN</sub> (µF) | C <sub>оит</sub> (µF) |

|-----------------------|----------------------|---------------------|---------------------|--------|------------|----------------------|-----------------------|

|                       | 3.3                  | 30                  | 10                  | 4.7    | 0.1        | 10                   | 22                    |

| 1.2                   | 5                    | 49.9                | 10                  | 6.8    | 0.1        | 10                   | 22                    |

|                       | 12                   | 52.3                | 3.9                 | 10     | 0.1        | 10                   | 22                    |

#### **Output Voltage Programming**

Output voltage can be set with a resistor divider feedback network between output and FB pin as shown in Figure 5 and Figure 6. Usually, a design is started by selecting lower resistor  $R_1$  and calculating  $R_2$  with the following equation:

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R_1}{R_2}\right)$$

(5)

where  $V_{RFF} = 0.83V$ .

To keep operating quiescent current small and prevent voltage errors due to leakage currents, it is recommended to choose  $R_1$  in the range of  $10k\Omega$  to  $100k\Omega.$

The error amplifier is normally able to maintain regulation since the synchronous output stage has excellent sink and source capability. However it is not able to regulate output when the FB pin is disconnected or when the output is shorted to a higher supply like input supply. Also when  $V_{\text{OUT}}$  is set to its minimum (0.83V) usually there is no voltage divider and  $V_{\text{OUT}}$  is directly connected to FB through a resistor (R<sub>1</sub> in the divider) and there is no resistor to ground (no R<sub>2</sub>). In such case and with no load, an internal current source of  $5\mu\text{A}\sim6\mu\text{A}$  from BOOT into the SW pin, which can slowly charge the output capacitor and pull  $V_{\text{OUT}}$  up to  $V_{\text{IN}}$ . Therefore a minimum load of at least  $10\mu\text{A}$  must be always present on  $V_{\text{OUT}}$  (for example, an  $80k\Omega$  resistor:  $0.83\text{V}/10.4\mu\text{A} = 80k\Omega$ ).

#### Inductor Selection

Higher operating frequency allows the designer to choose smaller inductor and capacitor values; however, the switching and gate losses are increased. On the other hand, at lower frequencies the current ripple  $(\Delta I_L)$  is higher, which results in higher light load losses. Use Equation 6 to calculate the required inductance  $(L_{\text{MIN}}).$  K is the ratio of the inductor peak-to-peak ripple  $(\Delta I_L)$  to the maximum operating DC current  $(I_{\text{OUT}}).$  The recommended selection range for K is between 0.2 and

0.4. Choosing a higher K value reduces the selected inductance, but a too high K factor may result in insufficient slope compensation. The inductance is selected based on the desired peak-to-peak ripple current ( $\Delta I_L$ ) for CCM. Equation 7 shows that  $\Delta I_L$  is inversely proportional to  $f_{SW} \times L$  and is increased at the maximum input voltage ( $V_{IN\_MAX}$ ). Therefore by accepting larger  $\Delta I_L$  values, smaller inductances can be chosen but the cost is higher output voltage ripple and increased core losses.

Inductor peak-current should never exceed the saturation even in transients to avoid over-current protection. Also inductor RMS rating should always be larger than operating RMS current even at maximum ambient temperature.

$$\Delta I_{L} = \frac{V_{OUT} \times (V_{IN\_MAX} - V_{OUT})}{V_{IN\_MAX} \times L \times f_{SW}}$$

(6)

$$L_{MIN} = \frac{V_{IN\_MAX} - V_{OUT}}{I_{OUT} \times K_{IND}} \times \frac{V_{OUT}}{V_{IN\_MAX} \times f_{SW}}$$

(7)

where  $K_{IND} = \Delta I_L / I_{OUT}$  (DC Current, MAX).

Note that it is generally desired to choose a smaller inductance value for faster transient response, smaller size, and lower DCR. On the other hand, if the inductance is too small, current ripple will increase which can trigger over-current protection. The larger the ripple of inductance current is, the larger the ripple of output voltage of output capacitor is. For peak-current mode control, it is recommended to choose large current ripple, because controller comparator performs better with higher signal to noise ratio. So, for this design example,  $K_{IND} = 0.4$  is chosen, and the minimum inductor value for 12V input voltage is calculated to be 5.1µH. The nearest standard value would be a 6.8µH ferrite inductor with a 2A RMS current rating and 2.5A saturation current that are well above the designed converter output current RMS and DC respectively.

# **APPLICATION INFORMATION (continued)**

#### **Bootstrap Capacitor Selection**

A 0.1µF ceramic capacitor with 16V or higher voltage rating must be connected between the BOOT-SW pin to provide the gate drive supply voltage for the high-side MOSFET. The bootstrap capacitor is refreshed when the high-side MOSFET is off and the low-side switch conducts. X7R or X5R dielectric types are recommended.

#### Input Capacitor Selection

The input capacitor also provides the high frequency switching transient currents. So, choosing a low-ESR and small size capacitor with high self-resonance frequency and sufficient RMS rating is necessary. Typically, 10µF high quality ceramic capacitor (X5R, X7R or better) with voltage rating twice the maximum input voltage is recommended for decoupling capacitor. If the source is away from the device (> 5cm), some bulk capacitances are also needed to damp the voltage spikes caused by the wiring or PCB trace parasitic inductances. The value for this capacitor is not critical but must be rated to handle the maximum input voltage including ripple.

In this example, one  $10\mu F/50V/X7R$  capacitor and a  $0.1\mu F$  ceramic capacitor placed right beside the device VIN and GND pins for very high-frequency filtering are used.

#### **Output Capacitor Selection**

This device is designed to be used with external LC filters. The minimum required capacitance to keep cost and size down and bandwidth high. The main parts for designing the output capacitance are output voltage ripple, loop stability and the voltage over/undershoot during load current transients. So,  $C_{\text{OUT}}$  should be chosen carefully. The output voltage ripple is determined of two factors. One is caused by the inductor current ripple going through the ESR of the output capacitors:

$$\Delta V_{OUT ESR} = \Delta I_L \times ESR = K_{IND} \times I_{OUT} \times ESR$$

(8)

The other part is caused by the inductor current ripple charging and discharging the output capacitors:

$$\Delta V_{\text{OUT\_C}} = \frac{\Delta I_{\text{L}}}{8 \times f_{\text{SW}} \times C_{\text{OUT}}} = \frac{K_{\text{IND}} \times I_{\text{OUT}}}{8 \times f_{\text{SW}} \times C_{\text{OUT}}}$$

(9)

These AC components are not in phase and the total peak-to-peak ripple is less than  $\Delta V_{OUT\ ESR}$  +  $\Delta V_{OUT\ C}$ .

Transient performance specification usually limits output capacitance if the system requires tight voltage regulation in presence of large current steps and/or fast slew rate. The output capacitor must provide the increased load current or absorb the excess inductor current (when the load current steps down) until the control loop can re-adjust the current of the inductor to the new load level. The control loop of regulator usually requires 8 or more clock cycles to adjust the inductance current to the new load level. The output capacitance must be as large as possible to provide a current difference of 8 clock cycles to keep the output voltage within the specified range. Equation 10 shows the minimum output capacitance required to specify output overshoot/undershoot.

$$C_{OUT} > \frac{1}{2} \times \frac{8 \times (I_{OH} - I_{OL})}{f_{SW} \times \Delta V_{OUT SHOOT}}$$

(10)

where:

$I_{\text{OL}}$  = Low level of the output current step during load transient.

$I_{\text{OH}}$  = High level of the output current during load transient.

$V_{OUT\ SHOOT}$  = Target output voltage over/undershoot.

For this design example, the target output ripple is 30mV. Assuming  $\Delta V_{\text{OUT\_ESR}} = \Delta V_{\text{OUT\_C}} = 30\text{mV}$ , and choosing  $K_{\text{IND}} = 0.4$ , Equation 8 requires ESR to be less than  $62.5\text{m}\Omega$  and Equation 9 requires  $C_{\text{OUT}} > 1.67\mu\text{F}$ . The target over/undershoot range of 5V output is  $\Delta V_{\text{OUT\_SHOOT}} = 5\% \times V_{\text{OUT}} = 250\text{mV}$ . From Equation 10,  $C_{\text{OUT}} > 16\mu\text{F}$ . So, in summary, the most stringent criteria for the output capacitor is transient constrain of  $C_{\text{OUT}} > 16\mu\text{F}$ . For the derating margin, one  $22\mu\text{F}$ , 10V, X7R ceramic capacitor with  $10\text{m}\Omega$  ESR is used.

# **APPLICATION INFORMATION (continued)**

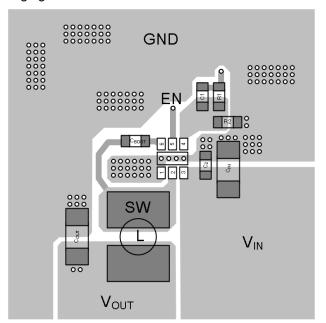

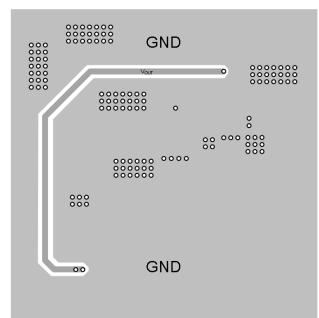

#### **Layout Guide**

Careful layout is always important to ensure good performance and stable operation to any kind of switching regulator. Place the capacitors close to the device, use the GND pin of the device as the center of star-connection to other grounds, and minimize the trace area of the SW node. With smaller transient current loops, lower parasitic ringing will be achieved.

Figure 7. Suggested PCB

Figure 8. Typical Application Circuit

# SGM61412

# **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| MAY 2022 - REV.A.1 to REV.A.2                                     | Page     |

|-------------------------------------------------------------------|----------|

| Updated Detailed Description and Application Information sections | 11 to 17 |

| AUGUST 2021 – REV.A to REV.A.1                                    | Page     |

| Added the SGM61412B section                                       | All      |

| Changes from Original (APRIL 2021) to REV.A                       | Page     |

| Changed from product preview to production data                   | All      |

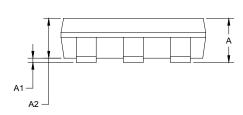

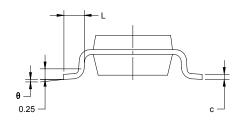

# PACKAGE OUTLINE DIMENSIONS TSOT-23-6

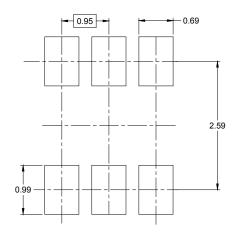

#### RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol | _         | nsions<br>meters | Dimensions<br>In Inches |       |  |

|--------|-----------|------------------|-------------------------|-------|--|

|        | MIN       | MIN MAX          |                         | MAX   |  |

| Α      |           | 1.000            |                         | 0.043 |  |

| A1     | 0.000     | 0.100            | 0.000                   | 0.004 |  |

| A2     | 0.700     | 0.900            | 0.028                   | 0.039 |  |

| b      | 0.300     | 0.500            | 0.012                   | 0.020 |  |

| С      | 0.080     | 0.200            | 0.003                   | 0.008 |  |

| D      | 2.850     | 2.950            | 0.112                   | 0.116 |  |

| E      | 1.550     | 1.650            | 0.061                   | 0.065 |  |

| E1     | 2.650     | 2.950            | 0.104                   | 0.116 |  |

| е      | 0.950 BSC |                  | 0.037                   | BSC   |  |

| L      | 0.300     | 0.600            | 0.012                   | 0.024 |  |

| θ      | 0°        | 8°               | 0°                      | 8°    |  |

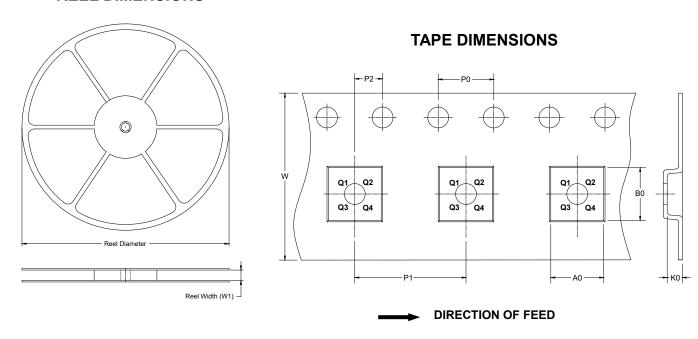

## TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TSOT-23-6    | 7"               | 9.5                      | 3.20       | 3.10       | 1.10       | 4.0        | 4.0        | 2.0        | 8.0       | Q3               |

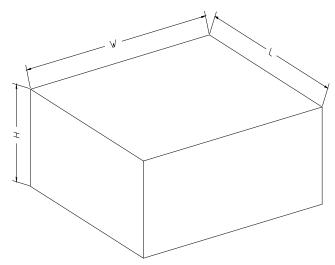

#### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type   | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |

|-------------|----------------|---------------|----------------|--------------|

| 7" (Option) | 368            | 227           | 224            | 8            |

| 7"          | 442            | 410           | 224            | 18           |